Ripple & Noise Technical Analysis: A Critical Power Indicator for System Stability

When selecting AC-DC or DC-DC power modules, engineers often focus on efficiency, output power, safety certifications, and protection features. However, one of the key parameters that truly determines signal integrity, system stability, and long-term reliability is Ripple & Noise.

Excessive Ripple & Noise can lead to:

- I/O false triggering on MCUs or FPGAs

- Unstable sensor readings and reduced ADC accuracy

- Reduced wireless communication sensitivity

- Motor vibration or speed instability

- Long-term electrical stress that shortens component lifespan

Therefore, understanding, measuring, and effectively reducing Ripple & Noise is essential in both power design and product selection.

What Are Ripple and Noise?

An ideal power supply would deliver a perfectly smooth DC output. In reality, the output voltage always contains superimposed waveforms of various frequencies, collectively referred to as Ripple & Noise.

- Ripple

Ripple is generated by the charging and discharging behavior of output filter components and by the switching topology itself. Its characteristics include:

- Periodic waveform caused by the switching frequency (tens of kHz to several hundred kHz)

- Predictable and repetitive waveform behavior

- Strongly influenced by output inductors, capacitor ESR/ESL, and control-loop characteristics

Conceptually: Ripple is the “periodic wave.”

- Noise

Noise consists of high-frequency voltage spikes generated by the fast switching transitions of power devices. It typically features:

- Frequency components up to the MHz range

- High-amplitude, irregular, and unpredictable spikes

- Sources include parasitic inductances/capacitances and cross-conduction effects

- Often the primary contributor to system instability

Conceptually: Noise is the “irregular spike.”

Why Does Ripple & Noise Affect System Reliability?

Different applications have different sensitivities, but common impacts include:

- MCU / DSP / FPGA — Unstable signals & false triggering

High-frequency noise disrupts logic circuits, causing ADC fluctuations or triggering errors. - RF Communication Modules (Wi-Fi / LTE / BLE / RFID) — Reduced sensitivity

Noise lowers SNR, affecting communication distance and stability. - Precision Sensors (load cell, optical, pressure) — Measurement errors

Even small ripple can shift sensor readings, reducing measurement accuracy. - Motor Drivers (Stepper / Servo) — Torque ripple & jitter

Ripple induces current oscillation, affecting motor stability and positioning. - System Lifespan — Long-term component degradation

Repeated noise spikes accelerate the aging of capacitors and driver ICs.

How Is Ripple & Noise Measured?

Ripple & Noise values listed in datasheets (in mVp-p) are typically measured under the following conditions:

- Oscilloscope bandwidth set to 20 MHz

Prevents high-frequency components from being filtered out. - Ground-spring measurement method

Minimizes additional noise introduced by test leads. - Adding 0.1 μF + 47 μF capacitors at the output

Simulates real-world load-side filtering conditions. - Testing at full load and half load

Ensures measurements reflect realistic operating conditions.

※ ARCH clearly defines measurement conditions in all datasheets to ensure accurate and consistent results for customers.

Main Design Factors Influencing Ripple & Noise

- Topology and Switching Method

Different architectures (Flyback / Forward / LLC) have inherently different ripple characteristics. - Output Filter Capacitors (ESR / ESL)

- Lower ESR → Lower ripple

- Higher ESL → Larger noise spikes

- PCB Layout (traces and grounding)

Smaller high-frequency current loops result in lower noise. - EMI Filter Design

Including common-mode inductors, differential filters, and Y capacitors. - Load Conditions

Dynamic load changes directly affect ripple and noise behavior.

How to Reduce Ripple & Noise: Practical Engineering Tips

- Add Output Filter Capacitors (47–220 μF)

Effectively reduces low-frequency ripple. - Add High-Frequency MLCCs (0.1 μF / 1 μF)

Suppresses MHz-range noise spikes. - Implement a π-filter (C-L-C)

Commonly used in RF, audio, and precision measurement systems. - Optimize PCB Grounding and Layout

- Separate analog ground and power ground

- Use star grounding

- Minimize high-frequency loop area

- Use an Isolated Power Module

Reduces noise coupling and improves system immunity. - Choose a Low-Noise Power Supply

High-quality power modules integrate superior filtering and control-loop designs to ensure lower ripple and noise across operating conditions.

Recommended Ripple & Noise Levels for Different Applications

| Application | Recommended R&N | Notes |

| Precision sensors / ADC | < 50 mVp-p | Highly noise-sensitive |

| MCU / Communication | < 80 mVp-p | Ensures stable signal operation |

| Medical (non-patient) | < 100 mVp-p | Emphasizes reliability |

| Industrial control / PLC | 100–150 mVp-p | Noisy operating environments |

| Motor control | 150–200 mVp-p | Less sensitive to noise |

Conclusion: ARCH Sets Higher Standards to Safeguard Your System Stability

Ripple & Noise is a critical yet often overlooked factor that directly affects system reliability. In applications such as precision sensing, smart manufacturing, AIoT, industrial control, and high-speed communication, excessive noise can lead to signal drift, false triggering, communication issues, motor instability, and even shortened system lifespan.

To address these challenges, ARCH has established Ripple & Noise standards that are significantly stricter than those required by most end-equipment—targeting approximately 1% of the rated output voltage. This requirement is fully integrated into our product development and production workflow:

- Design Stage: Layout optimization, grounding strategy, and component selection are all carried out with low-noise performance as a core objective.

- Verification Stage: Ripple & Noise is measured under standardized conditions (20 MHz bandwidth, 0.1 µF + 47 µF capacitors) to ensure each output meets specification.

- Production Quality Control: Before shipment, Ripple & Noise testing is performed following standardized procedures to ensure consistent and stable low-noise performance across all batches.

Through this rigorous process, every ARCH power module delivers low ripple, low noise, and high stability, helping customers achieve better system accuracy, reduced interference and malfunction risks, fewer service issues, and more reliable long-term operation.

If you are looking for a more stable, reliable, and long-lasting power solution, we invite you to explore ARCH’s product lineup and discover how our designs can enhance your system performance.

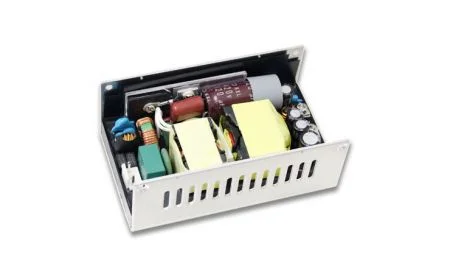

Explore More ARCH AC-DC Power Solutions

- Related Products

Ripple & Noise Technical Analysis: A Critical Power Indicator for System Stability | ARCH

The ARCH power supply blog shares practical guides on AC/DC design, EMC, safety approvals and thermal performance for real-world industrial and medical projects.

Each article is written for hardware engineers, project managers and buyers who need clear, vendor-backed explanations rather than generic theory.

Browse our latest posts to compare architectures, avoid common design mistakes and make more confident sourcing decisions for your next power platform.

Our Company Facts in Numbers

0

Years of Experience

0

Global Customers

0

Countries

0%

R&D Staff