Ripple & Noise (纹波与杂讯)技术解析:影响系统稳定性的关键电源指标

在挑选AC-DC 或DC-DC 电源模组时,多数工程师会优先查看效率、输出功率、安全认证与保护机制;但真正决定系统讯号品质、可靠度与长期寿命的核心指标之一,其实是Ripple & Noise(纹波与杂讯)。

过高的Ripple & Noise 可能造成:

- MCU 或FPGA 的I/O 误触发

- 感测器讯号不稳、ADC 精度下降

- 无线通讯灵敏度下降

- 马达抖动或转速不稳

- 长期累积电气应力、缩短元件寿命

因此,理解、量测并有效降低Ripple & Noise,是电源设计与产品选型中不可忽略的重要环节。

什么是Ripple(纹波)& Noise(杂讯)?

理想的电源应提供完全平滑的直流输出,但实际运作中,输出端会叠加不同频率的波动,统称Ripple & Noise。

-

Ripple(纹波)

由输出滤波元件的充放电行为与开关拓朴运作所产生,具有以下特性:

- 由开关频率造成的规律波形(数十kHz~数百kHz)

- 波形起伏规律、可预测

- 主要受输出电感、电容ESR/ESL、控制回路影响

概念化理解:Ripple 是规律的“波动”。

-

Noise(杂讯)

由高速开关元件的切换瞬间产生的尖峰电压(spike),特性如下:

- 频率可达MHz 等级

- 幅度大、不规则、较难预测

- 多由寄生电感、寄生电容、交叉导通所造成

- 通常是系统不稳定的最大干扰来源

概念化理解:Noise 是不规则的“尖峰”。

Ripple & Noise 为什么影响系统可靠度?

不同应用被干扰的敏感度不同,但影响方向大致如下:

-

MCU / DSP / FPGA — 讯号不稳、IO 误触发

高频杂讯会干扰逻辑层,使ADC 读值跳动或造成false triggering。 -

RF 通讯模组(Wi-Fi / LTE / BLE / RFID)— 灵敏度下降

杂讯会降低SNR,影响连线品质与通讯距离。 -

精密感测器(Load cell、光学、压力)— 量测误差放大

微小纹波就足以让讯号偏移,使量测精度降低。 -

马达驱动(Stepper / Servo)— 扭矩脉动、抖动

纹波会直接造成电流震荡,影响定位与稳定性。 -

整机寿命— 元件长期承受尖峰干扰

尖峰杂讯会加速电容、驱动IC 的老化。

Ripple & Noise 的典型量测方式

Datasheet 上标示的Ripple & Noise(mVp-p)通常依以下条件量测:

-

20 MHz 带宽示波器

防止示波器滤掉高频杂讯,使数据失真。 -

接地弹簧量测法

缩短接地导线避免引入额外Noise。 -

附加0.1 µF + 47 µF 电容

模拟真实负载端的滤波效果。 -

全负载/ 半负载测试

确保量测资料能反映实际运作情况。

※ ARCH 通常在Datasheet 内明确注明量测条件,确保客户在实际使用时结果一致。

影响Ripple & Noise 的主要设计因素

-

拓朴Topology 与开关方式

不同架构(Flyback / Forward / LLC)有不同的纹波特性。 -

输出滤波电容(ESR / ESL)

- ESR 越低→ 纹波越小

- ESL 越高→ 尖峰杂讯越大

-

PCB Layout(布线与接地)

高速电流环路越小,Noise 越低。 -

EMI 滤波设计

包含Y 电容、共模电感、差模滤波器等。 -

负载条件

不同负载会改变电源的动态反应,进而影响Ripple & Noise。

如何降低Ripple & Noise? (工程师实用改善指南)

-

在输出端增加滤波电容(47–220 µF)

改善低频Ripple。 -

增加高频MLCC(0.1 µF / 1 µF)

抑制MHz 等级尖峰杂讯。 -

依需求加入π 型滤波(CLC)

常用于音讯、RF、精密量测系统。 -

优化接地布局

- 模拟地与功率地分开

- 单点接地(Star grounding)

- 减少高速电流环路

-

使用带隔离的电源模组

降低杂讯耦合,提升整体系统稳定度。 -

选择更低噪声的电源模组

高品质电源具备更完整的EMI 与滤波设计,可提升整体系统抗干扰能力。

选型指南:不同应用建议的Ripple & Noise(mVp-p)

| 应用类型 | 建议R&N | 说明 |

| 精密感测器、ADC | < 50 mVp-p | 对噪讯极度敏感 |

| MCU / 通讯设备 | < 80 mVp-p | 确保讯号稳定 |

| 医疗(非病患接触) | < 100 mVp-p | 重视可靠性 |

| 工控/ PLC | 100–150 mVp-p | 工业环境杂讯多 |

| 马达控制 | 150–200 mVp-p | 相对较不敏感 |

结语: ARCH 以更严格的标准,守护您的系统稳定性

Ripple & Noise 是影响系统可靠度的隐形关键,无论是在精密感测、智慧制造、AIoT、工控通讯或高速运算领域,过高的输出噪讯都可能造成讯号偏移、误触发、通讯干扰或系统寿命缩短。

因此,ARCH 在产品设计上制定了比一般终端设备更严格的Ripple & Noise 标准—— 目标约为输出电压的1% 以内,并将此要求完整导入研发与生产流程:

- 设计阶段:以低噪讯作为核心目标进行layout、接地与滤波设计

- 验证阶段:依20 MHz、0.1µF + 47µF 标准测试条件进行量测

- 量产控管:出货前依标准化程序进行Ripple & Noise 品质检测

透过这套严谨流程,ARCH 提供的每款电源模组都能维持低纹波、低杂讯与高稳定度,大幅提升系统整体性能、减少异常与干扰,并降低后续维修与客诉成本。

若您正在寻找更稳定、更可靠、能长期运作的电源解决方案,欢迎造访ARCH 产品页,了解我们如何协助您的系统达到最佳表现。

探索更多翊嘉AC-DC 电源解决方案:点我前往官网产品页

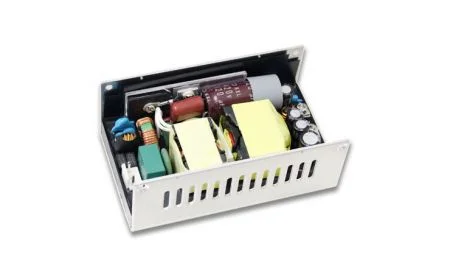

- 关联产品

翊嘉電子公司简介

翊嘉電子股份有限公司是台湾一家专业在高效电源解决方案的制造服务商。成立于西元1986年并拥有超过20年的AC-DC电源模组, AC-DC 封装电源模组, AC-DC 开关电源, AC-DC 电源供应器, AC-DC 开关电源模组, 超小型AC-DC 电源模组制造经验,翊嘉電子提供完整的产品组合,并通过ISO 9001、CE、UL、TUV 等多项国际认证,致力于持续创新、节能与永续发展。

关于翊嘉電子的优势数据

0

产业经验年资

0

全球客户

0

销售国家

0%

研发团队